# Memory-Model-Aware Analysis of Parallel Programs

PHD THESIS PROPOSAL

Vladimír Štill

# Abstract

Development of parallel programs comes with many pitfalls as it requires reasoning about interaction of threads and safety of communication. Furthermore, testing is not much helpful for bugs dependent on scheduling non-determinism. To make matters worse, contemporary hardware uses relaxed memory semantics: instructions can be reordered by out-of-order execution and memory effects can be further delayed by cache hierarchy. This means that the natural interleaving model of parallelism used both by developers and many formal analysis tools does not expose all possible executions of the program. The problem is further complicated by the fact that different hardware platforms have different memory models which allow various levels of instruction reordering.

This PhD thesis proposal is dedicated to the problem of analysis of parallel programs running on hardware with relaxed memory semantics. It first presents the state-of-the-art in description of memory models and in analysis techniques which take them into account. It further presents goals for the rest of my PhD studies, concretely devising methods for efficient analysis of C and C++ programs running under relaxed memory models. These analysis techniques should be applicable to unit tests of parallel synchronization primitives, data structures, and algorithms. All the techniques will be implemented in the DIVINE model checker. Finally, the thesis proposal summarises my achieved results.

# Keywords

relaxed memory, memory models, parallelism, software verification, program transformation, LLVM, C++, DIVINE, implementation

# Contents

| 1  | Intr                  | roduction                                               | 1         |

|----|-----------------------|---------------------------------------------------------|-----------|

| 2  | Relaxed Memory Models |                                                         | 5         |

|    | 2.1                   | Description of Memory Model Semantics                   | 6         |

|    | 2.2                   | Formalized Memory Models                                | 8         |

|    | 2.3                   | Memory Models and Compilers                             | 15        |

| 3  | Ana                   | alysis Techniques for Memory Models                     | 17        |

|    | 3.1                   | Decidability and Complexity                             | 17        |

|    | 3.2                   | Robustness Checking                                     | 19        |

|    | 3.3                   | Direct Analysis Techniques                              | 20        |

| 4  | Aim of the Work       |                                                         | <b>25</b> |

|    | 4.1                   | Objectives and Expected Results                         | 25        |

|    | 4.2                   | Time Plan                                               | 28        |

| 5  | Achieved Results 29   |                                                         |           |

|    | 5.1                   | Published Papers                                        | 29        |

| Bi | bliog                 | graphy                                                  | 33        |

| A  | Pub                   | olications                                              | 43        |

|    | A.1                   | Techniques for Memory-Efficient Model Checking of C and |           |

|    |                       | C++ Code                                                | 44        |

|    | A.2                   | Weak Memory Models as LLVM-to-LLVM Transformations .    | 59        |

|    |                       | Using Off-the-Shelf Exception Support Components in C++ |           |

|    |                       | Verification                                            | 71        |

|    | A.4                   | Model Checking of C and C++ with DIVINE 4               | 82        |

vi *CONTENTS*

# Chapter 1

# Introduction

Reasoning about the correctness of parallel programs is hard, even if we assume that every memory action a thread performs is visible to all other threads immediately, there is total ordering of these actions, and all loads read from the last write in this ordering. Sadly, this assumption of sequential consistency of the memory does not hold in practice as both hardware and compilers perform optimizations which disrupt it. These optimizations include instruction reordering in compilers and out-of-order processors and effects of cache hierarchies in the processors. These techniques are vital for fast execution of all programs, not just parallel ones. In the presence of these relaxations, memory changes can be observed in a different order by different threads. It is the responsibility of the programmer to ensure that the program executes correctly by enforcing ordering of some operations, for example using memory barriers and atomic instructions of a given processor architecture, or using higher level constructs of a given programming language.

In many programming languages, this problem is partially mitigated by the presence of higher level constructs such as mutexes (locks) or synchronized sections of code. These constructs, if used correctly, guarantee that the program will be executed as if running on hardware which preserves sequential consistency. Nevertheless, programmers who design these synchronization constructs, operating systems, and hi-performance parallel data structures have to be aware of memory relaxations arising from the particular memory model.

To complicate matters further, different hardware platforms perform different relaxations of memory accesses – for example, x86 and x86-64 (also known as AMD64) processors can only delay stores after loads, while ARM or POWER can also reorder writes with each other and reorder reads with writes arbitrarily (except for reordering of dependent writes). Each platform also comes with a specific set of atomic instructions and memory barriers, which can be used to enforce operation ordering. Therefore, in order to

be able to have the same code work on different platforms, it is useful to have support for enforcing memory operation ordering in the programming language itself. This support is also important as the compiler can reorder some operations while it optimizes the code and therefore it must be able to understand constructs that prevent such reordering, so they can prevent it both in the compiler and in the hardware.

Unfortunately, not all programming languages provide primitives related to memory relaxation or even define behaviour of parallel programs. For example, C and C++ had no support for parallel programming until the respective standards from the year 2011. In the older versions, parallelism was achieved only by means of libraries which provided thread manipulation and synchronization primitives (such as pthreads on POSIX systems) and memory ordering could have been controlled either by using these synchronization primitives or by compiler-provided language extensions. Apart from the lack of standardized and multi-platform parallel programming support, the problem of this approach is that it is not clear which ordering guarantees arise from the program's code. Other programming languages, such as Java, C#, C11, and C++11, have support for parallelism (including synchronization using mutexes and atomic variables) and their respective specifications describe what guarantees on memory operation ordering these languages provide. It is then the responsibility of the compiler (and virtual machine in the case of Java/C#) to ensure these guarantees are met on any supported platform.

In this situation, we believe that study of memory relaxations all the way from the code in a programming language<sup>1</sup> to the level of the hardware is important for the design of correct data structures and algorithms for parallel programs. Furthermore, we believe this study should produce both descriptions of memory behaviour of programming languages and hardware platforms as well as tools which can help developers who design data structures and algorithms for these platforms.

In my PhD research, I would like to primarily focus on analysis of parallel programs running on hardware with relaxed memory semantics. I would like to explore possibilities of efficient analysis of such programs which would be powerful enough to be usable to developers of hi-performance parallel data structures and algorithms. Such analysis needs to be able to handle unit tests of real-world parallel data structures under relaxed memory models. For these unit tests, it should be able to verify both unreachability of errors, as well as termination and preferably also general liveness properties

<sup>&</sup>lt;sup>1</sup>By programming language we understand higher-level languages in which code is mostly written by humans (e.g. C, C++, and Java) and distinguish them from assembly languages, which use platform-specific instructions and syntax, and from intermediate languages, which are used in some compilers mainly for platform-independent optimizations (e.g. LLVM IR).

(as given by linear temporal logic). Furthermore, the analysis should be parametrized by the memory model and should support various hardware memory models and the memory model of the programming language. As performance is often critical in parallel programs, I will focus on programs written in C and C++.

Providing a sound and complete decision procedure for memory models is not always possible, as all important problems are undecidable at least for some widespread memory models (more in Section 3.1). Nevertheless, the introduced methods should be designed so that they give high confidence in the correctness of analysed programs. The analysis should primarily be developed for the DIVINE model checker but should also be transferable also to other analysis tools.

The rest of this work is structured as follows: Chapter 2 describes prominent memory models used in both hardware and programming languages. Chapter 3 describes analysis and verification techniques for relaxed memory. These two chapters together give an overview of the state-of-the-art. Chapter 4 then presents aims of my future work and my time plan towards the thesis. Finally, Chapter 5 describes my research results in the area of analysis of parallel programs to date, including results not related to relaxed memory and Appendix A contains selection of my published papers.

# Chapter 2

# Relaxed Memory Models

The behaviour of a program in the presence of relaxed memory is described by the corresponding relaxed memory model. This memory model depends on the programming language of choice (as it can allow reordering of certain actions for the purpose of optimizations) and on the hardware on which the program is running. It also depends on the compiler (or interpreter or virtual machine) which is responsible for translating the program in a way that it meets the guarantees given in the specification of the programming language. We will abstract from the impact of the compiler and expect it to be correct in most of our considerations. We will also abstract from the impact of an operating system's scheduler which can move program threads between physical processing units, which could be visible in memory behaviour, but the operating system should make sure this effect is not visible.

In hardware, there are two main sources for the relaxed memory behaviour, both of them caused by the fact that memory is several orders of magnitude slower than the processor. One of these sources is the cache hierarchy, which tries to hide speed differences by storing parts of the data in caches. The other is out-of-order execution, which further improves speed by reordering the instructions and issuing instructions speculatively.

Depending on the implementation of these optimizations, different relaxations are observable. On x86, only store buffering (delaying of propagation of writes to the memory) is observable, while on ARM or POWER, reordering of all kinds of instructions is observable, as is branch prediction. A more detailed description of causes for memory relaxations (mainly originating from cache hierarchies) can be found in [McK10]. All processors with relaxed memory also provide instructions which allow the programmer to constrain relaxations: memory fences (or barriers) which prevent reordering and atomic instructions such as atomic compare-and-swap or atomic read-modify-write.

When dealing with the memory model of hardware, it is usually neither possible nor useful to discuss the behaviour of a concrete CPU, instead, we discuss the behaviour of a certain platform (e.g. Intel x86 or IBM POWER). There are at least two good reasons for this: first, results which take into account only the concrete CPU might not be applicable to any other CPU, even from the same family, and second, the exact architecture is usually kept secret by the company manufacturing those CPUs. For this reason, hardware memory models describe processor platforms and should over-approximate the behaviour of processors of a given platform and capture the intent of hardware designers to allow the results to remain relevant even for future processors. The over-approximation might be also needed to simplify the memory model in order to make the subsequent program analysis simpler.

Ideally, formalized memory models of hardware would be produced by the hardware manufacturers themselves, but this is often not the case. Instead, these memory models of contemporary platforms are usually created based on informal descriptions provided by the manufacturers, empirical testing of existing hardware, and discussion with the manufacturers [Sew+10; Sar+11; Flu+16].

Alternatively, one might describe a memory model of a programming language (or a compiler, if the programming language in question does not define memory behaviour of parallel programs). This would then allow the analysis of a program to reason about its behaviour on any platform on which it can be compiled (assuming the compiler is correct). Sadly, similarly to CPU platforms, programming languages usually lack a precise formal description of the memory model, see e.g. [Bat+11] for an analysis of a draft of the C++11 memory model. Furthermore, such specifications can be unnecessarily strict in some cases. For example, according to C++11, any parallel programs in which two threads communicate without the presence of locks or atomic operations have an undefined behaviour and therefore can have arbitrary outcome. Nevertheless, in practice, communication using volatile variables (and possibly compiler-specific memory fences) can work well with most compilers and is often used in legacy code written before C++11 (or C11 in the case of C) where there was no support for concurrency in the language.

In the following sections, we will first look into ways to describe memory models formally (Section 2.1). Then we will inspect important memory models of hardware and programming languages (Section 2.2). Finally, we will shortly discuss the impact of compiler optimizations on memory models (Section 2.3).

# 2.1 Description of Memory Model Semantics

As already noted, it is often the case that CPU architecture specifications or language specifications describe memory models informally. This can lead to imprecision when such specification is used as a basis for a program,

compiler or analyzer implementation. For this reason, it is useful to have formal semantics given to memory models.

The two main options used for the description of memory model semantics are axiomatic semantics, which is usually based on dependency relations between actions of the program, and operational semantics, which describes working of an abstract machine which implements a given memory model.

#### 2.1.1 Axiomatic Semantics

The axiomatic semantics of a memory model usually builds on relations between various memory-related actions of the program and properties of these relations. These relations are mostly partial orders and a sequence of operations usually adheres to a memory model if a union of a memory-modelspecific subset of these relations is acyclic (i.e. is a partial order). There are several notations for describing axiomatic semantics, which mostly differ in the names of defined relations and in some details in the description. The framework presented in [Alg+10] aims at description of different memory models in a unified way by a set of common dependency relations. In our figures, we will borrow some notation from this framework, namely the program order relation ( $\stackrel{\text{po}}{\longrightarrow}$ ) which orders actions performed by a single thread, the read-from relation  $(\stackrel{\mathrm{rf}}{\rightarrow})$  which connects a read with the store that saved the loaded value, and the from-read relation  $(\stackrel{\text{fr}}{\rightarrow})^1$  which connects read with the nearest store after the one read (i.e. with the store which will overwrite the read value). Furthermore, the write serialization relation  $(\stackrel{\text{ws}}{\longrightarrow})^2$  is notable for describing the guarantee given by all reasonable memory models: for each memory location there is a single total order of all writes to this location. That is, writes to a single location have to be observed in the same order by all threads. Other relations will be introduced as needed in the figures.

## 2.1.2 Operational Semantics

Alternatively, description of memory models can use operational semantics. Operational semantics describes behaviour of a program in terms of its run on an abstract machine, i.e. by describing the mechanisms which cause memory relaxations (usually in a largely simplified way which should closely match the behaviour of real hardware, but might use very different mechanisms). This usually makes operational semantics easier to understand by programmers and hardware designers and can also lead to a more direct implementation of certain analysis techniques.

<sup>&</sup>lt;sup>1</sup>In other works also *conflict relation*.

<sup>&</sup>lt;sup>2</sup>In other works also coherence relation.

## 2.1.3 Other Ways of Describing Memory Models

There are also some works which use different frameworks to describe memory models.

In [AM06] memory models are described in terms of two properties: allowed instruction reordering and *store atomicity*. Store atomicity roughly states that there is a global interleaving of all possibly reordered operations and the authors suggest that it is a desirable property of a memory model. Nevertheless, most architectural memory models lack store atomicity – both SPARC memory models (TSO/PSO/RMO) and x86-TSO allow loads to be satisfied from a store buffer, making stores observable in the issuing thread before they can be observed in other threads; POWER further allows independent stores to become visible in a different order in different threads.

The semantics given in [PS16] is based on event structures [NPW79] and considers all runs of the program at once. It is intended to allow reasoning about compiler optimizations. Due to its global view of the program, it is not clear if it can be used for efficient analysis of larger programs.

# 2.2 Formalized Memory Models

In this section we describe commonly used and formalized memory models. These memory models are usually derived from hardware or programming language memory models. In older works, most notable memory models (apart from Sequential Consistency) were memory models of the SPARC processors. These processors can be configured for different memory models (given in order from most strict to most relaxed): Total Store Order (TSO), Partial Store Order (PSO), Relaxed Memory Order (RMO) [SPA94]. Later memory models include Non-Speculative Writes (NSW) memory model presented in [Ati+12]. NSW is more relaxed than PSO but less relaxed than RMO and is notable because the reachability problem of programs with finite state processes under NSW is decidable while for RMO this problem is not decidable. This makes NSW significant even if it does not describe any hardware implementation. Further significant memory models include the x86 (and x86-64) memory model formalized as x86-TSO [Sew+10], POWER and ARM memory models, and memory models of certain programming languages, namely Java (Java was the first mainstream programming language with a defined memory model), C#, and C/C++11.

### 2.2.1 Sequential Consistency

Under sequential consistency (SC) all memory actions are immediately globally visible and therefore can be ordered by a total order (i.e. an execution of a parallel program is an interleaving of actions of its threads) [Lam79]. Furthermore, each load returns the last value written to its memory location in

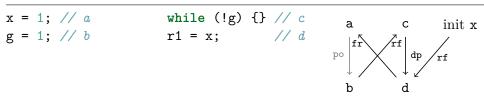

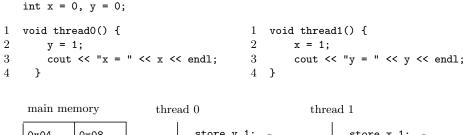

**Figure 2.1:** This code demonstrates behaviour which is allowed under TSO but is not allowed under SC. In the run illustrated on the right,  $\mathbf{x} = 1$  is executed first but the store is buffered and does not reach memory yet. Then  $\mathbf{r} = \mathbf{y}$  is executed, reading value 0 from  $\mathbf{y}$ . Then the second thread is executed fully and, since the update of  $\mathbf{x}$  was not yet propagated to the memory, it reads 0 from  $\mathbf{x}$ . Finally, the update of  $\mathbf{x}$  (originating from  $\mathbf{a}$ ) is performed.

this total order. In the operational semantics, SC corresponds to a machine without any caches and buffers where every store is immediately propagated to the global memory and every load reads directly from the memory. SC is the most intuitive and the strongest memory model and it is often used by program analysers, but it is not widely used in modern hardware. There are no fences in SC, as it has no need for them.

### 2.2.2 Total Store Order

Total Store Order (TSO) was introduced in the context of SPARC processors [SPA94]. It allows reordering of writes with subsequent reads originating from the same thread. Also, the thread that invokes a read can read value from a program-order-preceding write even if this write is not globally visible yet.

Operational semantics can be described by a machine which has an unbounded, processor-local FIFO store buffer in each processor. Writes are stored into the store buffer in the order in which they are executed. If a read occurs, the processor first consults its local store buffer and if it contains an entry for the loaded address it reads the newest such entry. If there is no such entry in the local store buffer, the value is read from the memory. At any point the oldest value from the store buffer can be removed from the buffer and stored to the memory. This way the writes in the store buffer are visible only to the processor which issued them until they are (non-deterministically) flushed to the memory. Machines which implement TSO-like memory models will usually provide memory barriers which flush the store buffer [McK10; Sew+10].

An example of TSO-allowed run which is not allowed under SC can be found in Figure 2.1.

Reachable r1 == 0?

**Figure 2.2:** This code demonstrates behaviour prohibited by TSO but allowed by PSO. In this case, the second thread waits for a guard g to be set and then attempts to read x. However, under PSO, writes to x and g can be reordered, resulting in action d reading from the initial value of x. Please note that PSO does not reorder reads and therefore c and d cannot be executed in inverted order.

#### 2.2.3 x86-TSO: x86 and x86-64 Processors

The memory model used by x86 and x86-64 processors is basically TSO with different fences and atomic instructions than in the SPARC implementation. The memory model is described informally in Intel and AMD specification documents and its formal semantics derived from these documents and experimental evaluation is described in the x86-TSO memory model [Sew+10]. The semantics of x86-TSO is formalized in HOL4 model and as an abstract machine.

On top of stores and loads which behave as under the TSO memory model, x86 has fence instructions, a family of read-modify-write instructions, and a compare-exchange instruction.

## 2.2.4 Partial Store Order

Partial Store Order (PSO) is similar to TSO and was also introduced by the SPARC processors [SPA94]. On top of TSO relaxations it allows reordering of pairs of writes which do not access the same memory location. Operational semantics corresponds to a machine which has a separate store buffer for each memory location. Again, a processor can read from its local store buffers but values saved in these buffers are invisible to other processors [SPA94]. PSO-mode SPARC processors include barriers for restoration of TSO as well as SC [SPA94]. An example of a PSO-allowed run which is not TSO-allowed can be found in Figure 2.2.

This memory model is supported for example by SPARC in PSO mode, but this is not a common architecture and configuration [SPA94; McK10], which means this memory model is mostly important theoretically.

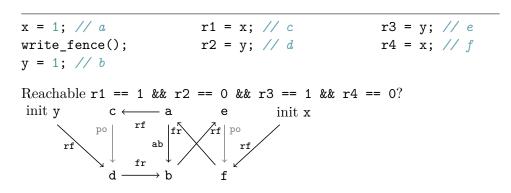

**Figure 2.3:** An example of behaviour allowed by NSW but not allowed by PSO. While the two writes are well ordered, the corresponding reads are not and since the memory model relaxes read-read ordering, they can observe values in different order. The write fence is not necessary, if it was not present the two threads would still not be able to observe different results under PSO, but it is used to demonstrate read reordering more clearly. The fence gives rise to the  $\stackrel{\text{ab}}{\Longrightarrow}$  relation.

## 2.2.5 Non-Speculative Writes

The Non-Speculative Writes (NSW) memory model, introduced in [Ati+12], is a memory model which is more relaxed than PSO but whose reachability problem for programs with a finite number of finite-state threads is still decidable. The operation model for NSW is also defined in [Ati+12]. It uses two levels of store buffers and a memory history buffer for reordering of reads.

On top of PSO relaxations, NSW allows reordering of reads with other reads and it is defined with read-read and write-write fences and atomic read-modify-write instructions. We show example of NSW behaviour which is not allowed by PSO in Figure 2.3. There are probably no processors which use NSW memory model – it is important theoretically for its decidability proofs.

### 2.2.6 Relaxed Memory Order

The relaxed memory order (RMO) further relaxes NSW by allowing all pairs of memory operations to be reordered provided they don't access the same memory location [SPA94]. Operational semantics for RMO usually allows instruction reordering in the machine, or involves guessing loaded value at the point of the load instruction and validating the guess later.

RMO is supported by SPARC processors. Examples of other hardware architectures with RMO-like memory models are POWER, ARM, and Alpha [McK10].

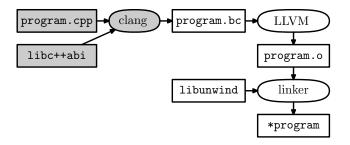

## 2.2.7 POWER Memory Model

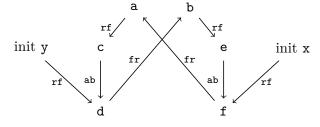

POWER is a very weak, RMO-like memory model in which it is possible to observe out-of-order execution as well as various effects of multi-level caches and cache coherence protocols [Sar+11; Mad+12]. For example, POWER allows independent writes to be propagated to different threads in different orders, or loads to be executed before control flow dependent loads (i.e. a load after a branch can be executed before the load which determines if the branch will be taken; this is not possible for writes). An example of POWER-allowed behaviour can be found in Figure 2.4.

The semantics of POWER processors is specified, apart from vendor documents, in both operational and axiomatic formalizations. In [Sar+11] POWER 7 memory model is described in the form of an abstract machine: it is an operational semantics, nevertheless, it is rather complicated due to subtleties of the architecture. This description was later extended in [Sar+12] to support POWER's load-reserve/store-conditional instructions which are used to implement low-level primitives such as compare-and-swap and atomic read-modify-write. An axiomatic semantics of POWER 7 is given in [Mad+12] and also in [Alg+10]. Nevertheless, [Sar+11] observes that while being in agreement with experimental results, [Alg+10] is not matching architectonic intent as well as their operational semantics. To our best knowledge, there is no formal description of the newer POWER 8 or POWER 9 architectures.

### 2.2.8 ARM Memory Model

The ARM memory model is similar to the POWER memory model, also exposing effects of out-of-order execution and cache hierarchy [Flu+16]. Nevertheless, there are important distinctions between ARM and POWER, both from the point of observable relaxations as well as hardware causes for these relaxations. It was formalized operationally in [Flu+16], building upon the same principles as the operational model for POWER introduced in [Sar+11]. This operational model describes the latest ARMv8/AArch64 64bit architecture and the work compares it to the POWER 7 architecture. There is also an older axiomatic model of ARMv7 given in [AMT14].

# 2.2.9 Memory Models of Programming Languages

Modern programming languages often acknowledge importance of parallelism and define memory behaviour of concurrent programs. Some programming languages give guarantees that programs which correctly use locks for synchronization observe sequentially consistent behaviour (the *data race free guarantee*). This holds for example for Java [AŠ07] and for the fragment of C++ without atomics weaker than sequentially consistent [TVD14] [ISO12, §1.10.21]. On top of that, some programming languages, such as C, C++,

Reachable r1 == 1 && r2 == 0 && r3 == 1 && r4 == 0?

**Figure 2.4:** An example of behaviour allowed by POWER, but not by NSW. There are 4 threads: two writers writing x or y and two readers reading both of these variables. The readers observe the updates in an inverted order (i.e. the third thread first reads the new value of x and then the old value of y, therefore it observes x first, but the last thread observes the new value of y and then the old value of x). The read fences do not help in this case, as the two writes happen in independent threads and therefore are not ordered in any way with respect to each other (the fences are used only to distinguish from NSW). The  $\xrightarrow{ab}$  relation is created by the fences.

and Java provide support for atomic operations which can be used for synchronization without locks if the platform they are running on supports it. C and C++ also support lower-level atomic operations with relaxed semantics which can be faster on platforms with relaxed memory.

### C and C++

In C and C++ prior to the 2011 standards, there was no support for threads and shared memory parallelism in the language. In these times creators of parallel programs were dependent on platform and compiler specific libraries and primitives, e.g. the pthread library for threading and \_\_sync\_\* family of functions for atomic operations in the GCC and Clang compilers.

The C++11 and C11 standards introduced support for threading and atomic operations to these languages. From the point of relaxed memory models, the interesting part of this is the support for atomic operations and fences.

The atomic operation library provides support for declaration of atomic variables which can be used in atomic operations, such as loads, stores, atomic read-modify-write, and compare-exchange. For any atomic operation, it is possible to specify the required ordering: C/C++ allows not only sequentially consistent atomic operations, but also weaker (low-level) atomic

operations which allows implementation of efficient parallel data structures in a platform-independent way.

The C++ memory model is not formalized in C++11 standard, an attempt to formalize it was given in [Bat+11], formalizing the N3092 draft of the standard [ISO10]. While this formalization precedes the final C++11 standard, it seems that there were no changes in the specification of atomic operations after N3092. Nevertheless, there are some differences between the formalization and N3092 (which are justified in the paper).

A notable feature of the C++ memory model is that any program which contains a data race on a non-atomic variable<sup>3</sup> has undefined behaviour. This means that synchronization is possible only by atomic variables and concurrency primitives such as mutexes and condition variables.

## LLVM

The LLVM compiler infrastructure [LLV17b] used by the clang compiler comes with its own low-level programming language. The LLVM memory model is derived from the C++11 memory model, with the difference that it lacks release-consume ordering and offers additional *Unordered* ordering which does not guarantee atomicity but makes results of data races defined [LLV17a]. The *Unordered* operations are intended to match semantics of the Java memory model for shared variables [LLV17a].

#### Java

The Java memory model is rather different from the C++11 one. Its primary goal is to ensure that programs which cannot observe data races under sequential consistency will execute as if running under sequential consistency (the data race free guarantee) [MPA05]. The primary means of synchronization in Java are mutexes (called monitors in Java), synchronized sections of code (which use monitors internally), and volatile variables, which roughly correspond to sequentially consistent atomics in C++11.

Furthermore, as Java strives to be memory safe, it also defines behaviour of programs with data races. This behaviour is rather peculiar, as it is primarily concerned with prohibiting *out-of-thin-air* values – values which, informally speaking, depend cyclically on themselves. These values are primarily prohibited to avoid forging pointers to invalid memory or memory which should be otherwise inaccessible to a given thread [MPA05].

Out-of-Thin-Air Values The problem with out-of-thin-air values is that it is sometimes hard to draw a line between behaviour in which value occurs

<sup>&</sup>lt;sup>3</sup>Data race is defined as two accesses to the same non-atomic variable, at least one of them being a write, which are not synchronized so that they cannot happen concurrently.

as a result of a well established compiler optimization and where it undesirably occurs out of pure speculation. To that end [MPA05] uses a definition which is based on *justifying executions* – a kind of inductive definition in which more relaxed executions are iteratively built from less relaxed executions. While this semantics intended to allow wide range of optimizations, it later turned out that it disallows certain reasonable optimizations [CKS07; ŠA08; TVD10].

Indeed the task of disallowing out-of-thin-air values while allowing optimizations is hard and there is no consensus on this topic. For example, the C++11 memory model allows these behaviours but at the same time states that implementations are discouraged to exhibit them [Bat+11]. The framework for description of hardware memory models introduced in [Alg+10] disallows out-of-thin-air values based on data and control dependencies. This is too strict for use in programming language memory models as these dependencies are changed by optimizers. It might be acceptable for hardware memory models where dependencies are more explicit and no current hardware exhibits this behaviour, but [Flu+16] mentions that this behaviour is intentionally left allowed by the ARMv8 memory model, in accordance with intents of the hardware architects. An alternative specification of semantics which aims at avoiding this problem was shown in [PS16], proposing new formalization of a fragment of C++11.

# 2.3 Memory Models and Compilers

When analysing programs in high level programming languages (as opposed to analysing assembly level programs), there can be substantially more relaxation than is allowed by the memory model of the hardware these programs target. The reason is that compilers are allowed to perform optimizations which reorder code or eliminate unnecessary memory accesses. As a result, a compiler can for example merge two loads from a non-atomic variable or assume a load which follows a store to the same memory location to yield the stored value. Further reordering is allowed as per-thread program order is not a total order for programs in languages such as C and C++ (e.g. order of evaluation of function arguments is not fixed by the standard in most cases).

If these optimizations should be taken into account, they complicate the analysis substantially. The two basic options for their handling include reasoning about all permitted reorderings (see e.g. [PS16]), or side stepping the problem by using the same optimizing compiler to produce code both for verification and for actual execution (e.g. by verifying the binary or the optimized intermediate representation of the compiler).

# Chapter 3

# Analysis Techniques for Memory Models

Analysis and verification of parallel programs is undoubtedly desirable and memory models play an important role in the correctness of these programs; therefore, many techniques exist for analysis of parallel programs under various memory models. In this chapter, we will first look into decidability of common verification problems under relaxed memory models and then we will review some of the approaches to the analysis.

These techniques can be split into two main areas. The first area focuses on verification adherence of a program to a certain memory model if it runs under other, weaker (more relaxed), memory model. For example, they can test whether a given program has no runs under TSO which would not be allowed under SC. Some of these techniques also support fence insertion to restrict behaviours to that of the stronger memory model.

The second category aims at checking correctness of a program (according to some property) under a relaxed memory model (e.g. checking for assertion safety or memory safety or checking of LTL properties). While the first category can be seen as a special case of the second, we consider the distinction notable as the techniques from the first category are usually not used to prove absence of certain types of erroneous behaviour, but assume that all relaxed behaviour is undesirable.

# 3.1 Decidability and Complexity

Right from the start it is important to note that even if we limit ourselves to programs with a finite number of finite-state threads/processes, there are important problems in widely-used memory models which are not decidable (while reachability under Sequential Consistency is in PSPACE for such programs [SC85]).

### 3.1.1 Reachability of Error State

Here we ask if the program can reach an error (or goal) state from its initial state. In practice, there can be multiple error states which are given by some property which can be evaluated on each state separately, e.g. we can look for assertion violations or memory errors.

According to [Ati+10], the problem of state reachability in concurrent programs with finite-state processes running under relaxed memory models is decidable for TSO and PSO memory models, but not decidable for RMO (and therefore also not decidable for POWER and ARM). The complexity of the state reachability in these programs under TSO and PSO is non-primitive recursive. In [Ati+12], these decidability findings are further refined: a more relaxed decidable memory model, Non-Speculative Writes (NSW) is identified, and stronger claim about undecidability is proven, showing that adding relaxation that allows reordering reads after subsequent writes to TSO brings undecidability.

The proofs in [Ati+10] use a very simple program model with a finite number of finite-state control units and simple memory actions. Furthermore, they assume that the number of memory locations and processes is fixed and that the data domain is finite. On the other hand, in practice both valid memory locations and processes can be created during the run of the program (and even though there is an upper bound on their number, this upper bound is not practical for the use in analysis).

## 3.1.2 Verification of Liveness Properties

Liveness properties described by Linear Temporal Logic (LTL) or Computational Tree Logic (CTL) are important class of properties often considered especially in connection with reactive systems and explicit-state model checking [CGP99, Chapter 3]. They allow users to specify properties such as reaction to a certain event or repeated occurrence of an event and they are evaluated on infinite runs of the program. With the automata-based approach to explicit-state model checking these problems are solved by solving repeated reachability of accepting states of Büchi product automaton derived from the program and the specification [BKL08, §5.2].

According to [Ati+10], repeated reachability, which can be used as a basis for verification of LTL properties, is not decidable even for TSO. Furthermore, from the construction of the reduction in the repeated reachability undecidability proof and from [AJ96] it follows that both LTL and CTL model checking problems are undecidable for TSO. Therefore LTL model checking is undecidable for all memory models more relaxed than SC shown in this work. For SC, it is well known that LTL model checking is in PSPACE for finite-state programs [SC85].

### 3.1.3 Verification of Absence of SC Violations

Here the question is whether a program, when run under a relaxed memory model, exhibits any runs not possible under SC. This problem is explored under many names, e.g. (TSO-)safety [BM08], robustness [BDM13; DM14], and stability [AM11].

Interestingly, [DM14] shows that even for the POWER memory model, checking robustness of programs with a finite number of finite-state threads is in PSPACE, using an algorithm based on reduction to language emptiness. For PSO and TSO, PSPACE algorithm for robustness is shown by [BSS11], this time the algorithm is based on monitoring of SC runs of the program. This shows that checking that a program does not exhibit relaxed behaviour is significantly simpler than checking if this behaviour can actually lead to an error.

# 3.1.4 Consequences of Decidability and Complexity Results

It can be seen that analysis of a program under a relaxed memory model is a hard task, much harder than for a program running under SC. For this reason most analysis techniques cannot be used to prove the absence of errors, or only in cases when the program is robust to the given memory model. In practice most analysis tools use some kind of constraining of the memory-model-induced reordering: for example bounding the number of instructions which can be reordered, or bounding the number of context switches.

# 3.2 Robustness Checking

As shown in the previous section, checking robustness (the absence of relaxed behaviour) is significantly less complex than verifying absence of errors in relaxed runs. For this reason, there is an interest in combination of verification under sequential consistency with a robustness checker [BM08]. This way, it is possible to check that program is correct under SC and whether all relaxed runs are equivalent to some SC runs. If both of these checks succeed, it can be concluded that the program is correct under a given relaxed memory model. However, the disadvantage of this technique is that for correctness analysis of parallel programs it can vastly over-approximate possible errors. In practice it is often desirable to allow relaxed behaviours, provided they do not lead to errors: a careful use of relaxed memory can yield much better performance than restricting the program to SC.

In [BM08], the SOBER tool, which allows detection of TSO violations, is presented. This tool works by monitoring sequentially consistent runs of the program and detecting violations which would occur under TSO. The

monitoring algorithm is based on vector clocks and axiomatic definition of TSO.

An alternative approach to checking robustness by monitoring SC runs is presented in [BSS11]. This approach allows checking robustness under both TSO and PSO and is built on the operational semantics of these memory models. This monitoring algorithm is implemented in the tool THRILLE and should be asymptotically faster than the one presented in [BM08] while also being sound and complete.

Another possibility for checking TSO robustness is to use *attacks*, a form of restricted out-of-order execution which witnesses SC violations. This approach is presented in [BDM13], together with an implementation in the TRENCHER tool which uses the SC model checker Spin [Hol97] as the backend for validation of attacks.

Restring programs running under the x86 or POWER memory models to SC behaviours is explored in [AM11]. The work also presents offence, a tool which inserts synchronization into x86 or POWER assembly to ensure stability.

Concerning stronger memory models, [DM14] shows an algorithm for checking robustness under POWER, but does not provide any implementation. The algorithm presented in this work also assumes that the number of processes is fixed and each process is a finite automaton, therefore it is not directly applicable to robustness checking of real-world programs.

For programming languages with the data race free guarantee, <sup>1</sup> data race freedom can be used as sufficient condition for robustness. The problem of data race detection is explored for example in [YGL04] for the Java Memory Model (JMM). In this case we ask if the program uses enough synchronization to avoid any data races. However, as the JMM defines data races in terms of SC executions, this work only formalizes SC. The entire program, memory constraints, and the specification is encoded as a constraint solving problem, which can be solved by a constraint solver, e.g. Prolog with finite domain data. This work is accompanied by the *DefectFinder* tool.

# 3.3 Direct Analysis Techniques

Many techniques for safety analysis of programs under relaxed memory models fall into the category of bug finding tools – such tools are unable to prove correctness in general, but they provide substantially better coverage of possible behaviours of parallel program than testing. This incompleteness is mostly caused by either bound on the number of instructions which can be reordered or number of context switches the program can do during any explored run.

<sup>&</sup>lt;sup>1</sup>Stating that data race free programs observe only sequentially consistent behaviours.

There are several reasons for this bounding; the obvious one is the time complexity of the analysis, but another important reason is that dealing with programs in programming languages is substantially more difficult than dealing with programs represented as a composition of finite-state processes (as assumed in the complexity analyses).

### Transformation-Based Techniques

A widely used family of methods for analysis of relaxed memory models is based on transformation of an input program P into a different program P' such that running P' under sequential consistency allows us to explore runs equivalent to running P under a more relaxed memory model. The main advantage of this approach is that it makes it possible to reuse existing analysis tools for sequentially consistent programs together with all the advancements in their development. In most cases the transformation also includes some way of bounding relaxation and therefore this allows exploring only a subset of runs of P. Further under-approximation might be caused by the used SC analyser (e.g. when bounded model checker is used as a backend).

In [Alg+13] a transformation-based technique for the x86, POWER, and ARM memory models is presented. This transformation is parametrized and can be tweaked to implement different memory models. It is implemented in the goto-instrument tool for instrumentation of goto-programs. As goto-programs can be created by translation from C, this work primarily focuses on C programs. The output of the transformation is a goto-program which can be verified directly by some analysers, or translated back to C. The technique presented in this work is sound, but not complete (due to buffer bounding and possible incompleteness in the backend). It is also not clear if it can cover all cases of delaying reads after writes. The work is accompanied by Coq proofs matching the axiomatic semantics to the operational semantics used for the implementation.

Another approach to program transformation is taken in [ABP11], in this case the transformation uses context switch bounding but not buffer bounding and it uses additional copies for shared variables for TSO simulation. Two options for the transformation are presented, in the first one the total number of context switches is limited, in the second there is a limited number of context switches the value can be delayed for, but the overall analysis is not context-switch-bounded. There is no tool accompanying this publication – the experiments were performed using manually translated C programs.

In [Abd+17] the context-bounded analysis using transformation is applied to the POWER memory model. The resulting program uses nondeterminism heavily to guess the results of a sequence of instructions which is later checked. It uses bounded model checker CBMC as a backend. The

publication is accompanied by the power2sc tool which implements the transformation of C programs.

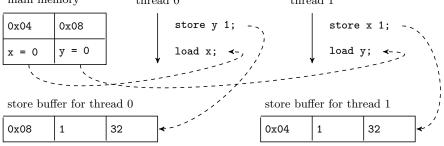

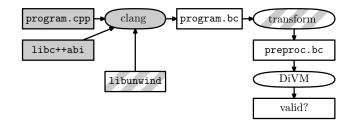

Our own work in [ŠRB16b] presents a transformation of LLVM bitcode to simulate buffer-bounded TSO runs. It targets DIVINE and therefore C and C++ programs.

#### Stateless Model Checking

Stateless Model Checking methods are intended for safety analysis of terminating programs in real-world programming languages [God97]. They employ Dynamic Partial Order Reduction (DPOR) to avoid exploring equivalent runs of the program [FG05] and the works concerning relaxed memory models in this setting often discuss interlay between DPOR and relaxed memory model in length.

A stateless model checking approach to the analysis of programs running under the C++11 memory model (with the exception of release-consume synchronization) is presented in [ND13]. It uses custom implementation of C++ thread and atomic libraries to produce binaries which perform the analysis. It lazily builds relations between memory operations in the form of a modification order graph. This representation prevents exploration of infeasible executions as well as unnecessary distinction between equivalent executions. Furthermore, as the C++ memory model allows reordering of reads with future operations, the authors propose to simulate this by propagating stored values to previous loads and validating this speculation (which does not simulate out-of-thin-air values). The paper includes a long discussion on features of the C++ memory model and the corresponding implementation in CDSCHECKER, which is usable for (small) unit tests of concurrent data structures written in C11 or C++11.

In [ZKW15] the authors focus mostly on modelling of TSO and PSO and its interplay with DPOR. They combine modelling of thread scheduling nondeterminism and memory model nondeterminism using store buffers to a common framework. This is done by adding store buffers to the program and adding shadow thread for each store buffer which is responsible for flushing contents of this buffer to the memory. The proposed approach is implemented in the tool rInspect, which is an LLVM-based stateless model checker which supports both unbounded store buffers and buffer bounding (however, as it is a stateless model checker, it works only on programs which terminate).

Another approach to combining TSO and PSO analysis with stateless model checking is presented in [Abd+15]. In this work executions are represented by chronological traces which capture dependencies required to represent interaction between memory actions. These chronological traces are acyclic relations and therefore can be used for DPOR, including the optimal DPOR which explores exactly one execution in the equivalence class

of the partial order [Abd+14]. The advantage of this approach is that for robust programs, using the optimal DPOR algorithm with chronological traces should produce the same number of executions under SC as under relaxed memory model. The proposed approach is implemented in an LLVM-based tool Niddhugg, which supports analysis of C programs with pthreads parallelism and with a bounded execution length.

#### **Unbounded Methods**

There are also analysis methods which aim to be able to discover any memory-model-related bugs, regardless of number of instructions being reordered or number of context switches.

An approach to verification of programs under TSO, which uses unbouded store buffers, is presented in [LW10]. It uses store buffers represented by automata and leverages cycle iteration acceleration (for cycles involving changes in only one store buffer) to get representation of store buffers on paths which would form cycles if values in store buffers were disregarded. It uses sleep set POR to reduce state space. The provided tool targets a modified Promela language [Hol97]. Since the cycle acceleration is limited to changes in one store buffer, it is not clear if the algorithm is guaranteed to terminate.

Another unbounded approach is presented in [Bou+15] – it introduces TSO behaviours lazily by iterative refinement, and while it is not complete, it should eventually find all errors. This work is based on the robustness checker presented in [BDM13] and uses it to detect runs to which relaxed behaviour should be added. The work is accompanied by an implementation in the tool TRENCHER.

#### Other Methods

In [PD95], the SPARC hierarchy of memory models (TSO, PSO, RMO) is modelled using encoding from assembly to  $\text{Mur}\varphi$  [Dil96]. The encoding allows all reordering of instructions allowed by a given memory model up to a certain reordering bound. This work targets small synchronization primitives such as spin locks.

In [HR06] an explicit state model checker for C# programs (supporting subset of C#/.NET bytecode) which uses the .NET memory model is presented. The verifier first verifies program under SC and then it explores additional runs allowed under the .NET memory model. It can also insert barriers into the program to avoid relaxed runs which violate a given property. The implementation of the exploration algorithm uses a list of delayed instructions to implement instruction reordering. While the authors mention that the number of reordered instructions is not bounded, they do not discuss how this approach works for programs with cycles.

The work [Dan+13] presents an approach for verification of (potentially infinite state space) programs under TSO and PSO using predicate abstraction. The paper first shows that it is not possible to use traditional predicate abstraction to produce a boolean program and then verify this boolean program using weak memory semantics. Instead, they propose a schema which first verifies the program under SC and then extrapolates predicates from the SC run to verify a transformed version of the original program which has store buffers explicitly encoded. The store buffers are bounded in this transformation. Implementation in the tool CUPEX is also provided.

A completely different approach is taken in [TVD14]. This work introduces a separation logic GPS, which allows proving properties about programs using (a fragment of) the C11 memory model. That is, this work is intended for manual proving of properties of parallel programs, not for automatic verification. The memory model is not complete, it lacks relaxed and consume-release accesses. Another fragment of the C11 memory model is targeted by the RSL separation logic introduced in [VN13].

# Chapter 4

# Aim of the Work

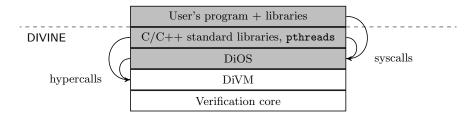

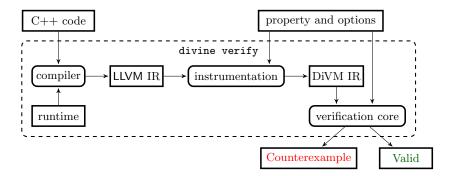

Overall, the aim of my PhD research is to devise methods for efficient analysis of C and C++ programs running under relaxed memory models. These methods should also be implemented and thoroughly evaluated, aiming at real-world usability. Namely, I would like to make it possible to apply relaxed-memory-aware analysis to unit tests of nontrivial parallel data structures and algorithms. The implementation will be primarily working with the DIVINE model checker [Bar+17].

# 4.1 Objectives and Expected Results

# 4.1.1 An LLVM-Based Program Transformation for Analysis of Relaxed Memory Models

A large number of verifiers and analysers with support for parallel programs lack support for relaxed memory models and assume sequential consistency. While it is possible to extend these verifiers to relaxed memory models directly in many cases, we believe that an easier and more versatile path lies in transformation of the input formalism for these analysers, as done for example by [Alg+13] or [Abd+17]. This way, the input program is transformed into another program which, when run under SC, simulates runs of the original program under a given relaxed memory model.

The most promising approach seems to be the use of the LLVM Intermediate Representation (LLVM IR) as the source and the target for the transformation. LLVM IR is widely used both by compilers (namely the clang compiler which can be used to compile C, C++, and Objective C on all major operating systems) and by a growing number of analysers with support for parallelism, for example DIVINE [Bar+17], SMACK [RE14], VVT [GLW16], Skink [Cas+17], and Nidhugg [Abd+15]. Furthermore, CPAchecker [BK11] has support for parallelism [BF16] and there are plans to add support for LLVM IR to it. Similarly, CBMC [CKL04] has support for parallelism and

planned support for LLVM. Also, LLVM IR can be rather easily transformed as it is used for optimizations in the LLVM framework.

One of the advantages of the program transformation approach is that the same transformation can be used for many analysers. The transformation works by replacing memory operations with either fragments of code or calls to functions which provide implementation of a given operation under a relaxed memory model. This also means that the same transformation, but with different implementations of memory operations, can be used for evaluation of different memory models and modes of their simulation.

An initial LLVM transformation for relaxed memory models was developed for [ŠRB16b] and later extended for [Šti16]. This transformation is now being updated to remove its dependence on a DIVINE-specific API and make its interface more general to work with different memory model implementations.

Furthermore, there are many options in optimization of the transformation, e.g. it is not necessary to transform memory operations for which it can be proven statically that they only access thread-local data. The first of my aims is therefore finishing this program transformation and its optimizations. The transformation will be used as a basis for implementation of memory-model-aware analysis in DIVINE and possibly other verifiers.

# 4.1.2 An Efficient Support for Non-Speculative Writes Memory Model

The program transformation needs to be accompanied by implementation of memory model operations (memory model runtime). The existing implementations for DIVINE [ŠRB16b; Šti16] support either TSO or a subset of the C++11 memory model without read reordering, both of which use buffer bounding to limit the state space explosion and achieve decidability while keeping the implementation simple.

I would like to implement a framework for simulation of various memory models. The first step in this direction will be to design an efficient operational model for the Non-Speculative Writes memory model. This operational model should be designed so that it can be efficiently implemented and provide good performance for verification.

The NSW memory model was chosen as it is decidable for programs with a finite number of finite-state threads, it is more relaxed than PSO, and it should be possible to implement it reasonably efficiently. To the best of our knowledge, the only operational semantics for NSW is given in [Ati+12] where it is introduced. However, while sufficient for proving its decidability, this semantics is not efficient for verification as it needs to resolve ordering of memory events eagerly, which leads to a lot of branching in the explored state space. It also includes storing complete snapshots of memory in form of history buffers. Instead, we would like to resolve ordering lazily only when

actually needed, which should improve scalability of the analysis and to save only relevant parts of memory history.

At first, we will use bounded data structures in the implementation of NSW support. Therefore, the resulting analysis algorithm will not be able to prove the absence of bugs as the number of instructions to be reordered will be bounded (but no other imprecisions will be introduced by this approach). Nevertheless, we believe this approach is reasonable as it can uncover a large number of errors which would otherwise be hard to find.

# 4.1.3 Heuristically-Directed Exploration Algorithm for Analysis under Relaxed Memory Models

An important aspect of usability of automatic verification and analysis techniques such as model checking is their ability to produce a property violation witness (counterexample) in case a property violation is found. However, usability of these counterexamples depends a lot on the exploration strategy employed by the analyser. For relaxed memory models, it is desirable that counterexamples which contain minimum possible number of deviations from sequential consistency are found first.

Furthermore, it is expected that by directing exploration to find less relaxed runs first, the algorithm will (on average) run faster for programs which contain errors. It might be also possible to employ heuristics to direct relaxations so that relaxed behaviour is first applied on variables on which it is more likely to cause property violations. Another possibility is using robustness-based heuristics and employ relaxed memory semantics only when needed, similar to [Bou+15].

## 4.1.4 Analysis of Very Weak Memory Models

The POWER and ARM memory models (which are quite similar) are important as they are very weak and there is increasing number of devices which use ARM processors and a good number of hi-performance devices powered by POWER. However, these memory models come with relaxations such as writes which can propagate in different order to different processors and reordering of loads with succeeding writes which can lead to seemingly cyclic dependencies. For this reason, these memory models are more subtle than NSW and require a more advanced analysis.

The C11 and C++11 standards came with a memory model designed to allow for an efficient multi-platform implementation of parallel primitives, even on very relaxed platforms such as POWER/ARM. Therefore, the C++11 memory model is as over-approximation of the POWER/ARM memory models in the context of C/C++ programs, in the sense that all behaviours possible under POWER/ARM are also possible under the C++11 memory model. A very similar memory model is also used by the LLVM

intermediate language. As DIVINE is an analyzer for C/C++, it is natural to have support for verification of programs under this memory model.

## 4.1.5 Techniques for Unbounded Memory Model Analysis

Up to this point I expect to allow only bounded instruction reordering. However, in order to increase coverage of our analysis, I would like to investigate techniques which allow unbounded reordering. Such techniques could use some form of symbolic encoding of delayed memory operations, such as automata-based encoding introduced in [LW10] (which supports only TSO), or they could use abstractions. Another possibility is using SMT-based symbolic encoding. All of these approaches will likely also require changes to the verification algorithm and therefore will not be implemented purely as program transformations accompanied by memory model runtime.

## 4.2 Time Plan

The plan of the rest of my PhD study and research activities is following:

Now – January 2018 Extension of the relaxed memory support in DI-VINE to the NSW memory model and design of verification-friendly semantics for NSW.

January 2018 Doctoral exam and defense of this thesis proposal.

- February 2018 June 2018 Development of heuristically directed search algorithm for verification under relaxed memory models in DIVINE.

- June 2018 November 2018 Extension of relaxed memory support to more relaxed memory models such as C++, POWER and ARM memory models, including development of transformation-friendly semantics of these memory models.

- **December 2018 July 2019** Investigation and design of techniques for unbounded verification of programs running under relaxed memory models.

August 2019 - January 2020 Text of the PhD thesis.

January 2020 The final version of the thesis.

# Chapter 5

# Achieved Results

My work so far has been mostly concerned with analysis of parallel programs and the DIVINE model checker [Bar+17]. It started during my bachelor studies with techniques for compression of state space, which resulted in the publication [RŠB15]. During my master's study, my work included heuristics for state space exploration [ŠRB14] and transformations of LLVM Intermediate Representation [ŠRB16b; Šti16]. These transformations included optimizations which can lead to more efficient verifications and transformations for relaxed memory models.

During my PhD work, I first focused mostly on general verification of parallel C and C++ programs. This included revised support for the C++ exceptions in DIVINE [ŠRB17] and a lot of work on the new version of DIVINE which mostly had character of implementation and resulted in a tool paper [Bar+17].

# 5.1 Published Papers

Jiří Barnat, Luboš Brim, Vojtěch Havel, Jan Havlíček, Jan Kriho, Milan Lenčo, Petr Ročkai, Vladimír Štill, and Jiří Weiser. "DiVinE 3.0 – An Explicit-State Model Checker for Multithreaded C & C++ Programs". In: Computer Aided Verification. Vol. 8044. Lecture Notes in Computer Science. Springer Berlin Heidelberg, 2013, pp. 863–868. DOI: 10.1007/978-3-642-39799-8\_60 [Bar+13]

Tool paper for DIVINE 3, I have minor contribution to the implementation of DIVINE 3 as described in this paper.

• Vladimír Štill, Petr Ročkai, and Jiří Barnat. "Context-Switch-Directed Verification in DIVINE". in: *Mathematical and Engineering Methods in Computer Science*. Vol. 8934. Lecture Notes in Computer Science. Springer International Publishing, 2014, pp. 135–146. DOI: 10.1007/978-3-319-14896-0\_12 [ŠRB14]

This paper shows that directing search of an explicit-state model checker to first explore runs with low number of context switches can improve performance of the verifier as well as the counterexamples. I have made implementation and evaluation for this paper as well as written part of the text. I have also presented this paper on the MEMICS 2014 conference.

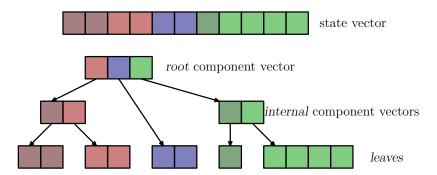

Petr Ročkai, Vladimír Štill, and Jiří Barnat. "Techniques for Memory-Efficient Model Checking of C and C++ Code". In: Software Engineering and Formal Methods. Vol. 9276. Lecture Notes in Computer Science. Springer International Publishing, 2015, pp. 268–282. DOI: 10.1007/978-3-319-22969-0\_19 [RŠB15]

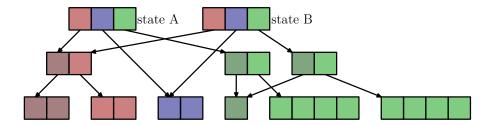

This paper describes techniques which lead to better memory efficiency of verification of parallel programs in an explicit-state model checker. These techniques include a tree-based compression scheme for state space storage and a custom allocation schema. I have made part of the implementation (concerning the compression), full evaluation and part of the text. I have also presented this paper on the SEFM 2015 conference.

Jiří Barnat, Petr Ročkai, Vladimír Štill, and Jiří Weiser. "Fast, Dynamically-Sized Concurrent Hash Table". In: Model Checking Software (SPIN 2015). Vol. 9232. Lecture Notes in Computer Science. Springer International Publishing, 2015, pp. 49–65. DOI: 10.1007/978-3-319-23404-5\_5 [Bar+15]

This paper describes efficient design of a concurrent hash table used in DIVINE. I have minor contributions to this paper.

Vladimír Štill, Petr Ročkai, and Jiří Barnat. "Weak Memory Models as LLVM-to-LLVM Transformations". In: Mathematical and Engineering Methods in Computer Science, Revised Selected Papers. Vol. 9548. Lecture Notes in Computer Science. Springer International Publishing, 2016, pp. 144–155. DOI: 10.1007/978-3-319-29817-7\_13 [ŠRB16b]

This paper describes the approach to analysis of programs under the TSO memory model using LLVM transformation. I am the main author of this paper, I have made most of the design and implementation, full evaluation, and most of the text. I have also presented this paper on the MEMICS 2015 conference.

Jiří Barnat, Ivana Černá, Petr Ročkai, Vladimír Štill, and Kristína Zákopčanová. "On Verifying C++ Programs with Probabilities". In: ACM Symposium on Applied Computing. 2016, pp. 1238–1243. DOI: 10.1145/2851613.2851721 [Bar+16]

This paper describes chaining of DIVINE (which was extended to allow annotation of edges with probabilities) with the PRISM model checker to allow probabilistic analysis. I have provided small part of the implementation (concerning export of state space from DIVINE) and text concerning this part for the paper.

Vladimír Štill, Petr Ročkai, and Jiří Barnat. "DIVINE: Explicit-State LTL Model Checker". In: Tools and Algorithms for the Construction and Analysis of Systems. Berlin, Heidelberg: Springer Berlin Heidelberg, 2016, pp. 920–922. DOI: 10.1007/978-3-662-49674-9\_60 [ŠRB16a]

Competition contribution for SV-COMP 2016 [Bey16]. This paper shortly describes DIVINE and the specifics of applying it to the concurrency category of SV-COMP. I am the main author of this paper, I have written most of the text as well as implemented all modifications of DIVINE which were needed for participation in SV-COMP 2016. I have also had a short presentation of this paper in the SV-COMP session of the ETAPS/TACAS 2016 conference.

• Jan Mrázek, Martin Jonáš, Vladimír Štill, Henrich Lauko, and Jiří Barnat. "Optimizing and Caching SMT Queries in SymDIVINE". in: Tools and Algorithms for the Construction and Analysis of Systems. Berlin, Heidelberg: Springer Berlin Heidelberg, 2017, pp. 390–393. DOI: 10.1007/978-3-662-54580-5\_29 [Mrá+17]

Competition contribution for SV-COMP 2017 [Bey17]. This paper shortly describes the SymDIVINE tool which combines explicit and symbolic approach to verification of parallel programs. I have made minor contributions to this paper.

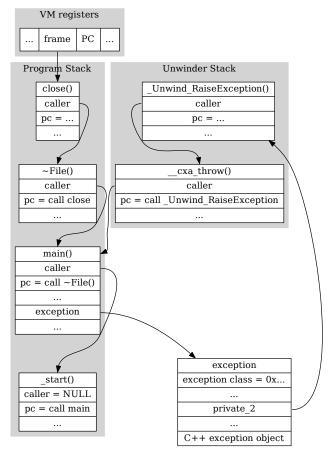

Vladimír Štill, Petr Ročkai, and Jiří Barnat. "Using Off-the-Shelf Exception Support Components in C++ Verification". In: Software Quality, Reliability and Security (QRS). IEEE, July 2017, pp. 54–64. DOI: 10.1109/QRS.2017.15 [ŠRB17]

This paper describes the approach we took towards verification of C++ code with exceptions in DIVINE 4. We show that carefully selecting which components of existing implementations and libraries to reuse and which to reimplement allowed us to provide full C++ exception support in DIVINE without much cost in terms of runtime performance, implementation effort or increase of complexity of the verifier.

I am the main author of this paper: I have written most of the text and implementation for exception support in DIVINE 4 as well as performed the evaluation for this paper. I have also presented this paper on the QRS 2017 conference. The paper and its presentation was awarded best paper award.

• Zuzana Baranová, Jiří Barnat, Katarína Kejstová, Tadeáš Kučera, Henrich Lauko, Jan Mrázek, Petr Ročkai, and Vladimír Štill. "Model Checking of C and C++ with DIVINE 4". In: *Automated Technology for Verification and Analysis*. Vol. 10482. Lecture Notes in Computer Science. 2017. DOI: 10.1007/978-3-319-68167-2\_14 [Bar+17]

Tool paper describing architecture of DIVINE 4 and new features of this version. I have written most of the text for this paper.

# **Bibliography**

- [Abd+14] Parosh Abdulla, Stavros Aronis, Bengt Jonsson, and Konstantinos Sagonas. "Optimal Dynamic Partial Order Reduction". In: Principles of Programming Languages. POPL '14. San Diego, California, USA: ACM, 2014, pp. 373–384. DOI: 10.1145/2535838.2535845.

- [Abd+15] Parosh Aziz Abdulla, Stavros Aronis, Mohamed Faouzi Atig, Bengt Jonsson, Carl Leonardsson, and Konstantinos Sagonas. "Stateless Model Checking for TSO and PSO". In: *Tools and Algorithms for the Construction and Analysis of Systems*. Berlin, Heidelberg: Springer Berlin Heidelberg, 2015, pp. 353–367. DOI: 10.1007/978-3-662-46681-0\_28.

- [Abd+17] Parosh Aziz Abdulla, Mohamed Faouzi Atig, Ahmed Bouajjani, and Tuan Phong Ngo. "Context-Bounded Analysis for POWER". In: *Tools and Algorithms for the Construction and Analysis of Systems*. Berlin, Heidelberg: Springer Berlin Heidelberg, 2017, pp. 56–74. DOI: 10.1007/978-3-662-54580-5\_4.

- [ABP11] Mohamed Faouzi Atig, Ahmed Bouajjani, and Gennaro Parlato. "Getting Rid of Store-Buffers in TSO Analysis". In: *Computer Aided Verification*. Berlin, Heidelberg: Springer Berlin Heidelberg, 2011, pp. 99–115. DOI: 10.1007/978-3-642-22110-1\_9.

- [AJ96] Parosh Aziz Abdulla and Bengt Jonsson. "Undecidable verification problems for programs with unreliable channels". In: *Information and Computation* 130.1 (1996), pp. 71–90.

- [Alg+10] Jade Alglave, Luc Maranget, Susmit Sarkar, and Peter Sewell. "Fences in Weak Memory Models". In: Computer Aided Verification. Berlin, Heidelberg: Springer Berlin Heidelberg, 2010, pp. 258–272. DOI: 10.1007/978-3-642-14295-6\_25.

- [Alg+13] Jade Alglave, Daniel Kroening, Vincent Nimal, and Michael Tautschnig. "Software Verification for Weak Memory via Program Transformation". In: *European Symposium on Programming*. Berlin, Heidelberg: Springer Berlin Heidelberg, 2013, pp. 512–532. DOI: 10.1007/978-3-642-37036-6\_28.

- [AM06] Arvind Arvind and Jan-Willem Maessen. "Memory Model = Instruction Reordering + Store Atomicity". In: ACM SIGARCH Computer Architecture News 34.2 (May 2006), pp. 29–40. ISSN: 0163-5964. DOI: 10.1145/1150019.1136489.

- [AM11] Jade Alglave and Luc Maranget. "Stability in Weak Memory Models". In: *Computer Aided Verification*. Berlin, Heidelberg: Springer Berlin Heidelberg, 2011, pp. 50–66. DOI: 10.1007/978-3-642-22110-1\_6.

- [AMT14] Jade Alglave, Luc Maranget, and Michael Tautschnig. "Herding Cats: Modelling, Simulation, Testing, and Data Mining for Weak Memory". In: *ACM Transactions on Programming Languages and Systems* 36.2 (July 2014), 7:1–7:74. ISSN: 0164-0925. DOI: 10.1145/2627752.

- [AŠ07] David Aspinall and Jaroslav Ševčík. "Formalising Java's Data Race Free Guarantee". In: *Theorem Proving in Higher Order Logics*. Berlin, Heidelberg: Springer Berlin Heidelberg, 2007, pp. 22–37. DOI: 10.1007/978-3-540-74591-4 4.

- [Ati+10] Mohamed Faouzi Atig, Ahmed Bouajjani, Sebastian Burckhardt, and Madanlal Musuvathi. "On the Verification Problem for Weak Memory Models". In: *Principles of Programming Languages*. POPL '10. Madrid, Spain: ACM, 2010, pp. 7–18. DOI: 10.1145/1706299.1706303.

- [Ati+12] Mohamed Faouzi Atig, Ahmed Bouajjani, Sebastian Burckhardt, and Madanlal Musuvathi. "What's Decidable about Weak Memory Models?" In: European Symposium on Programming. Berlin, Heidelberg: Springer Berlin Heidelberg, 2012, pp. 26–46. DOI: 10.1007/978-3-642-28869-2\_2.

- [Bar+13] Jiří Barnat, Luboš Brim, Vojtěch Havel, Jan Havlíček, Jan Kriho, Milan Lenčo, Petr Ročkai, Vladimír Štill, and Jiří Weiser. "DiVinE 3.0 An Explicit-State Model Checker for Multithreaded C & C++ Programs". In: Computer Aided Verification. Vol. 8044. Lecture Notes in Computer Science. Springer Berlin Heidelberg, 2013, pp. 863–868. DOI: 10.1007/978-3-642-39799-8\_60.

- [Bar+15] Jiří Barnat, Petr Ročkai, Vladimír Štill, and Jiří Weiser. "Fast, Dynamically-Sized Concurrent Hash Table". In: *Model Checking Software (SPIN 2015)*. Vol. 9232. Lecture Notes in Computer Science. Springer International Publishing, 2015, pp. 49–65. DOI: 10.1007/978-3-319-23404-5\_5.

- [Bar+16] Jiří Barnat, Ivana Černá, Petr Ročkai, Vladimír Štill, and Kristína Zákopčanová. "On Verifying C++ Programs with Probabilities". In: *ACM Symposium on Applied Computing*. 2016, pp. 1238–1243. DOI: 10.1145/2851613.2851721.

- [Bar+17] Zuzana Baranová, Jiří Barnat, Katarína Kejstová, Tadeáš Kučera, Henrich Lauko, Jan Mrázek, Petr Ročkai, and Vladimír Štill. "Model Checking of C and C++ with DIVINE 4". In: Automated Technology for Verification and Analysis. Vol. 10482. Lecture Notes in Computer Science. 2017. DOI: 10.1007/978-3-319-68167-2\_14.

- [Bat+11] Mark Batty, Scott Owens, Susmit Sarkar, Peter Sewell, and Tjark Weber. "Mathematizing C++ Concurrency". In: *Principles of Programming Languages*. POPL '11. Austin, Texas, USA: ACM, 2011, pp. 55–66. DOI: 10.1145/1926385.1926394.

- [BDM13] Ahmed Bouajjani, Egor Derevenetc, and Roland Meyer. "Checking and Enforcing Robustness against TSO". In: European Symposium on Programming. Berlin, Heidelberg: Springer Berlin Heidelberg, 2013, pp. 533–553. DOI: 10.1007/978-3-642-37036-6\_29.

- [Bey16] Dirk Beyer. "Reliable and Reproducible Competition Results with BenchExec and Witnesses (Report on SV-COMP 2016)". In: Tools and Algorithms for the Construction and Analysis of Systems. Berlin, Heidelberg: Springer Berlin Heidelberg, 2016, pp. 887–904. DOI: 10.1007/978-3-662-49674-9\_55.

- [Bey17] Dirk Beyer. "Software Verification with Validation of Results". In: Tools and Algorithms for the Construction and Analysis of Systems. Berlin, Heidelberg: Springer Berlin Heidelberg, 2017, pp. 331–349. DOI: 10.1007/978-3-662-54580-5\_20.

- [BF16] Dirk Beyer and Karlheinz Friedberger. "A Light-Weight Approach for Verifying Multi-Threaded Programs with CPAchecker". In: *Mathematical and Engineering Methods in Computer Science*. 2016, pp. 61–71. DOI: 10.4204/EPTCS.233.6.

- [BK11] Dirk Beyer and M. Erkan Keremoglu. "CPAchecker: A Tool for Configurable Software Verification". In: Computer Aided Verification. Berlin, Heidelberg: Springer Berlin Heidelberg, 2011, pp. 184–190. DOI: 10.1007/978-3-642-22110-1\_16.

- [BKL08] Christel Baier, Joost-Pieter Katoen, and Kim Guldstrand Larsen. *Principles of model checking*. MIT press, 2008.